# **FPGA Express**

Справочное руководство по VHDL

# СОДЕРЖАНИЕ

| ГЛАВА 1. ИСПОЛЬЗОВАНИЕ FPGA EXPRESS C VHDL             | 6  |

|--------------------------------------------------------|----|

| Языки аппаратного описания                             | 6  |

| Типичные применения HDL                                |    |

| ПРЕИМУЩЕСТВА HDL                                       |    |

| VHDL                                                   |    |

| ПРОЦЕДУРА ПРОЕКТИРОВАНИЯ FPGA EXPRESS                  |    |

| ИСПОЛЬЗОВАНИЕ FPGA Express для компиляции проекта VHDL |    |

| МЕТОДОЛОГИЯ ПРОЕКТИРОВАНИЯ                             |    |

| ГЛАВА 2. СТИЛИ ОПИСАНИЯ                                |    |

|                                                        |    |

| ИЕРАРХИЯ ПРОЕКТА                                       |    |

| Типы данных                                            |    |

| ПРОЕКТНЫЕ ОГРАНИЧЕНИЯ                                  |    |

| Выбор регистра                                         |    |

| Асинхронные проекты                                    |    |

| Языковые конструкции                                   | 11 |

| ГЛАВА 3. ОПИСАНИЕ ПРОЕКТОВ                             | 12 |

| Operation a VIIIDI                                     | 12 |

| Объекты VHDL<br>Конструкции VHDL                       |    |

| · ·                                                    |    |

| Объекты                                                |    |

| Архитектуры                                            |    |

| Конфигурации                                           |    |

| Процессы                                               |    |

| ПодпрограммыБлоки объявлений                           |    |

| Определение проектов                                   |    |

|                                                        |    |

| Объектные спецификацииОбъектные архитектуры            |    |

| Объектные ирхитектурыОбъектные конфигурации            |    |

| Ооъектные конфигурации<br>Подпрограммы                 |    |

| Поопрограммы                                           |    |

| Объявления типов                                       |    |

| Объявления поотинов                                    |    |

| Объявления сигналов                                    |    |

| Функции разрешения                                     |    |

| Функции ризрешения<br>Объявления переменных            |    |

| Структурное проектирование                             | 30 |

| Использование компонентов аппаратного уровня           |    |

| Компонентные объявления                                |    |

| Оператор реализации компонента                         |    |

| Технологически независимая реализация компонента       |    |

|                                                        |    |

| ГЛАВА 4. ТИПЫ ДАННЫХ                                   | 35 |

| Перечисляемые типы                                     | 35 |

| Перегрузка перечисления                                | 36 |

| Кодирование перечисления                               | 36 |

| Значения кодов перечисления                            |    |

| Целые типы                                             | 38 |

| Типы массивов                                          | 38 |

| Ограниченный массив                                    |    |

| Неограниченный массив                                  |    |

| Атрибуты массива                                       | 39 |

| Типы запись                                            |    |

| ПРЕДОПРЕДЕЛЕННЫЕ ТИПЫ ДАННЫХ VHDL                      |    |

| Tun данных BOOLEAN                                     |    |

| Тип данных BIT                                         |    |

| Tun данных CHARACTER                                   |    |

| Tun данных INTEGER                                            |    |

|---------------------------------------------------------------|----|

| Tun данных NATURAL                                            |    |

| Tun данных POSITIVE                                           |    |

| Тип данных STRING                                             |    |

| Тип данных BIT_VECTOR                                         |    |

| НЕПОДДЕРЖИВАЕМЫЕ ТИПЫ ДАННЫХ                                  | 44 |

| Физические типы                                               | 44 |

| Типы с плавающей точкой                                       | 44 |

| Типы доступа                                                  |    |

| Файловые типы                                                 | 44 |

| ТИПЫ ДАННЫХ SYNOPSYS                                          | 44 |

| Подтипы                                                       | 44 |

| ГЛАВА 5. ВЫРАЖЕНИЯ                                            | 45 |

| Операторы                                                     | 16 |

|                                                               |    |

| Логические операторы                                          |    |

| Операторы сравнения                                           |    |

| Операторы сложения                                            |    |

| Унарные (знаковые) операторы                                  |    |

| Операторы умножения                                           |    |

| Смешанные арифметические операторы                            |    |

| Операнды                                                      |    |

| Битовая ширина операндов                                      |    |

| Вычисляемые операнды                                          |    |

| Литералы                                                      | 55 |

| Идентификаторы                                                |    |

| Индексные имена                                               | 57 |

| Скользящие имена                                              | 58 |

| Записи и поля                                                 | 59 |

| Множества                                                     | 60 |

| Атрибуты                                                      | 61 |

| Вызовы функций                                                | 62 |

| Определенные выражения                                        | 62 |

| Преобразования типов                                          |    |

| ГЛАВА 6. ПОСЛЕДОВАТЕЛЬНЫЕ ОПЕРАТОРЫ                           | 64 |

| Операторы присваивания                                        | (5 |

|                                                               |    |

| Назначаемые указатели                                         |    |

| Простые имена-указатели                                       |    |

| Индексные имена-указатели                                     |    |

| Скользящие указатели                                          |    |

| Поля-указатели                                                |    |

| Множества-указатели                                           |    |

| ОПЕРАТОР ПРИСВАИВАНИЯ ПЕРЕМЕННОЙ                              |    |

| ОПЕРАТОР ПРИСВАИВАНИЯ СИГНАЛА                                 |    |

| Присваивание переменной                                       |    |

| Присваивание сигнала                                          |    |

| Оператор іг                                                   |    |

| Вычисляемое условие                                           |    |

| Использование оператора if для реализации регистров и защелок | 71 |

| Оператор case                                                 | 71 |

| Использование различных типов выражений                       |    |

| Недопустимые операторы case                                   |    |

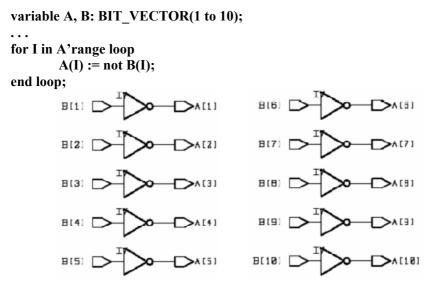

| Операторы Loop                                                | 73 |

| Onepamop loop                                                 | 74 |

| Onepamop while loop                                           | 74 |

| Onepamop for loop                                             |    |

| OHEPATOP NEXT                                                 | 76 |

| Оператор ехіт                                                 | 77 |

| Подпрограммы                                                  | 78 |

| Вызовы подпрограмм                                            | 79 |

| OHEPATOP RETURN                                                   | 81  |

|-------------------------------------------------------------------|-----|

| Размещение подпрограмм в компоненты (объекты)                     |     |

| Оператор Wait                                                     | 84  |

| Реализация синхронной логики                                      | 85  |

| Отличия комбинационных и последовательных процессов               | 87  |

| Offepatop null                                                    | 89  |

| ГЛАВА 7. ПАРАЛЛЕЛЬНЫЕ ОПЕРАТОРЫ                                   | 90  |

|                                                                   |     |

| ОПЕРАТОРЫ PROCESS.                                                |     |

| Пример комбинационного процесса                                   |     |

| Пример последовательного процесса                                 |     |

| Управляемые сигналы                                               |     |

| Oператор block                                                    |     |

| Параллельные вызовы процедур                                      |     |

| Условное присваивания сигналу                                     |     |

| условное присваивание сигналуВыборочное присваивание сигналу      |     |

| Компонентные реализации                                           |     |

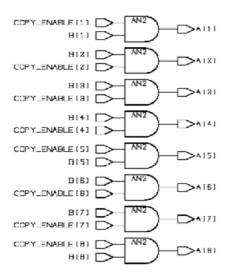

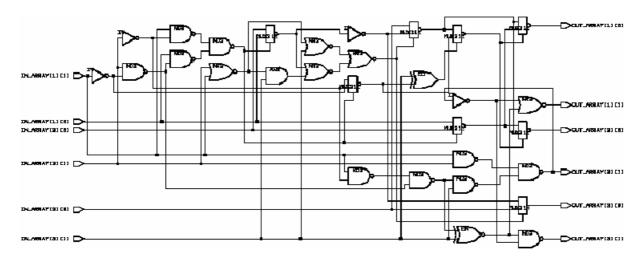

| Операторы generate                                                |     |

| Onepamop for generate                                             |     |

| Onepamop if generate                                              |     |

|                                                                   |     |

| ГЛАВА 8. РЕАЛИЗАЦИЯ РЕГИСТРОВ И ТРЕТЬЕГО СОСТОЯНИЯ                | 104 |

| РЕАЛИЗАЦИЯ РЕГИСТРОВ                                              | 104 |

| Использование реализаций регистров                                |     |

| Задержки в регистрах                                              |     |

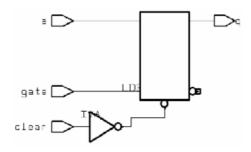

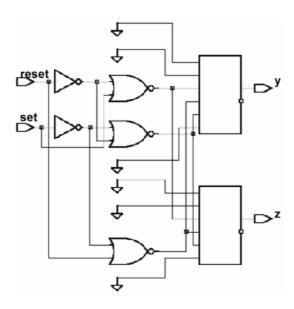

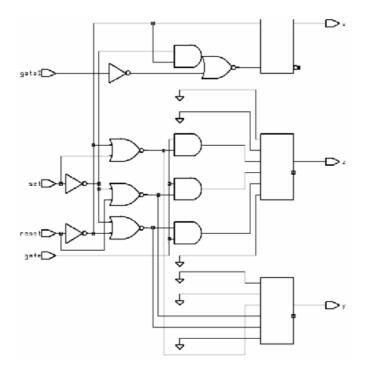

| Описание защелок                                                  |     |

| Описание триггеров                                                |     |

| Атрибуты                                                          | 113 |

| Реализация защелок и триггеров в FPGA Express                     | 123 |

| Эффективное использование регистров                               | 124 |

| Реализация третьего состояния                                     |     |

| Присваивание значения Z                                           | 127 |

| Защелкивающиеся переменные с третьим состоянием                   | 128 |

| ГЛАВА 9. ДИРЕКТИВЫ FPGA EXPRESS                                   | 129 |

| Нотация для директив FPGA Express                                 | 130 |

| Директивы FPGA Express                                            |     |

| Директивы запуска и останова трансляции                           |     |

| Директивы функции разрешения                                      |     |

| Директивы импликации компонента                                   |     |

| ГЛАВА 10. БЛОКИ ОБЪЯВЛЕНИЙ SYNOPSYS                               | 132 |

|                                                                   |     |

| БЛОК ОБЪЯВЛЕНИЙ STD_LOGIC_1164<br>БЛОК ОБЪЯВЛЕНИЙ STD_LOGIC_ARITH |     |

| Использование блока объявлений                                    |     |

| Использование олока объявлений                                    |     |

| Типы данных                                                       |     |

| Функции преобразования                                            |     |

| Арифметические функции                                            |     |

| Функции сравнения                                                 |     |

| Функции сдвига                                                    |     |

| Ampuóym ENUM ENCODING                                             |     |

| pragma built in                                                   |     |

| Лиректива translate off                                           |     |

| БЛОК ОБЪЯВЛЕНИЙ STD_LOGIC_MISC                                    |     |

| <br>ГЛАВА 11. КОНСТРУКЦИИ HDL                                     |     |

| ПОДДЕРЖИВАЕМЫЕ КОНСТРУКЦИИ VHDL                                   |     |

| Поддерживаемые конструкции <b>V По</b> С                          |     |

| троектные еоиницыТипы данных                                      | 145 |

| Ооъявления                   | 140 |

|------------------------------|-----|

| Спецификации                 |     |

| Имена                        |     |

| Операторы                    |     |

| Операнды и выражения         |     |

| Последовательные операторы   |     |

| Параллельные операторы       |     |

|                              |     |

| Предопределенная среда языка | 149 |

# Глава 1. Использование FPGA Express c VHDL

FPGA Express транслирует и оптимизирует описания VHDL во внутренний формат , эквивалентный уровню примитивных логических элементов. Этот формат затем компилируется в технологию FPGA.

Для работы с VHDL вам необходимо ознакомиться со следующими понятиями:

- Языки аппаратного описания

- VHDL

- FPGA Express

- Использование FPGA Express

- Модель процесса проектирования

Министерство обороны США разработало *VHSIC HDL* (VHDL) в 1982 году как часть программы развития сверх высокоскоростных ИС (VHSIC). VHDL описывает поведение, функции, входы и выходы цифровой схемы. VHDL, по стилю и синтаксису, аналогичен современным языкам программирования, однако включает много специфических аппаратных конструкций. FPGA Express читает и анализирует поддерживаемый синтаксис VHDL. В главе 11 перечислены все конструкции VHDL и уровни поддержки Synopsys для каждой конструкции.

# Языки аппаратного описания

Языки аппаратного описания (HDL) используются для описания архитектуры и поведения дискретных электронных систем. Эти языки разработаны для построения все более и более сложных проектов. Часто проводят историческую аналогию на предмет того , как могут называться программные языки описания , от машинных кодов (транзисторы и пайка) к ассемблерным языкам (списки цепей) и далее , к языкам высокого уровня (HDL).

HDL-ориентированные системы наиболее полезны при разработке больших проектов , когда несколько разработчиков или даже несколько команд работают совместно. HDL обеспечивают структурное программирование. После того , как приняты основные архитектурные решения , а основные компоненты и связи между ними идентифицированы , работа над подпроектами может происходить совершенно независимо.

# Типичные применения HDL

HDL обычно поддерживают смешанные описания, в которых структурные конструкции или списки цепей могут соединяться с алгоритмическими описаниями и описаниями поведения. При наличии таких смешанно-уровневых возможностей вы можете описывать архитектуру системы на высшем уровне абстракции; затем проект детализируется по нарастающей для частного компонентно-уровневого выполнения. В качестве альтернативы вы можете прочитать описание проекта HDL в FPGA Express, а затем заставить компилятор автоматически синтезировать выполнение на уровне логических примитивов.

# Преимущества HDL

Методология проекта , использующего HDL , имеет несколько фундаментальных преимуществ над традиционной компонентно-уровневой методологией проектирования. Среди этих преимуществ необходимо отметить следующие :

• Вы можете очень рано проверить функциональные возможности проекта и немедленно промоделировать его, записанный на HDL. Моделирование проекта на таком высшем уровне до трансляции в элементарное исполнение позволяет протестировать многие архитектурные и проектные решения.

- FPGA Express обеспечивает логический синтез и оптимизацию, так что вы можете автоматически преобразовать описание VHDL в исполнение элементарного уровня для выбранной технологии. Такая методология устраняет вышеупомянутые узкие места компонентного уровня и уменьшает время проектирования, а также количество ошибок, вносимых при ручной трансляции программы VHDL в конкретные элементы. С помощью логической оптимизации FPGA Express вы можете автоматически преобразовать синтезированный проект в наименьшую и наискорейшую схему. Кроме того, вы можете назначить информацию, полученную при синтезе и оптимизации схем, вновь описанию VHDL, что, возможно, приведет к более точной подстройке архитектурных решений.

- Описания HDL обеспечивают технологически независимую документацию проекта и его функциональных возможностей. Эти программы читаются и понимаются гораздо легче, чем списки цепей или схемы. Вследствие того, что начальное HDL описание проекта является технологически независимым, вы можете затем использовать его для генерации проектов с различной технологией, не затрагивая при этом оригинальную.

- VHDL, как и большинство языков высокого уровня, производит жесткую проверку типов. Компоненты, тип которых объявлен четырехбитовым сигналом, не могут соединяться с трех- или пятибитовым сигналом; такое несогласование приведет к ошибке при компиляции. Если диапазон переменных определен от 1 до 15, то ошибка возникнет при назначении им значения 0. Некорректное использование типов, как это будет показано, является основным источником ошибок при составлении описаний. Проверка типов обнаруживает такие ошибки даже перед генерацией проекта.

### **VHDL**

VHDL является одним из многих языков аппаратного описания , широко распространенных в настоящее время. VHDL является стандартным языком HDL в соответствии с IEEE (IEEE Standard 1076 , принят в 1987) , а также Министерством Обороны США (MIL-STD-454L).

VHDL делит *объекты* (компоненты , схемы или системы) на внешние или видимые (обладающие именами и связями) и внутренние или невидимые (алгоритмы и исполнение). После того , как вы определили внешний интерфейс с объектом , другие объекты могут использовать его по мере собственного создания. Такая концепция внутреннего и внешнего взглядов является центральной при рассмотрении системных проектов VHDL. По отношению к остальным , объект определяется своим поведением и связями. Вы можете исследовать альтернативные исполнения (*архитектуры*) объекта без изменения остальной части проекта.

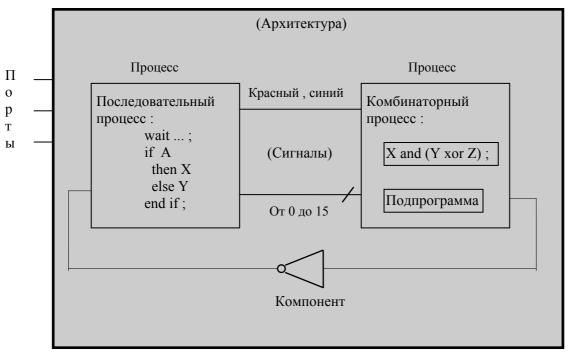

После того , как вы создали объект в одном из проектов , вы можете использовать его по мере необходимости в других проектах. Кроме того , вы можете создавать библиотеки объектов для применения во многих проектах или семействах проектов. Аппаратная модель VHDL показана на рис.1-1.

Объект VHDL (проект) имеет один или более входов , выходов или *портов* ввода-вывода , которые соединяются с соседними системами. Объект сам по себе состоит из совокупности соединенных между собой объектов , *процессов* и *компонентов* , которые работают совместно. Каждый объект определяется частной *архитектурой* , которая составлена из конструкций VHDL , таких как арифметические , сигнальные или компонентные реализации.

В VHDL независимые *процессы* моделируют поведение последовательных (тактируемых) схем, использующих триггера и защелки, и комбинаторных (не тактируемых) схем, использующих только логические элементы. Процессы могут определяться и называться *подпрограммами* (подпроектами). Процессы соединяются друг с другом с помощью *сигналов* (проводников). Сигнал имеет источник (формирователь), один или более приемников и определяемый пользователем *тип* например, «цвет» или «числа от 0 до 15».

VHDL обеспечивает широкий набор конструкций. С помощью VHDL вы можете описать дискретные электронные системы различной сложности (системы, платы, чипы, модули) с различными уровнями абстракции.

### Объект

Puc.1-1 Аппаратная модель VHDL

Конструкции языка VHDL подразделяются на три категории в зависимости от уровня абстрагирования : *поведенческая* , *поток данных* и *структурная*. Эти категории можно описать следующим образом :

- поведенческая (behavioral)

- Функциональные или алгоритмические аспекты проекта , выраженные в виде последовательного процесса VHDL.

- поток данных (dataflow)

- Просмотр прохождения данных через весь проект, от входа к выходу. Работа в данном случае определяется в терминах набора преобразований данных, выраженных в виде параллельных утверждений.

- структурная (structural)

- Просмотр, наиболее приближенный к аппаратному обеспечению; модель, в которой связаны все компоненты проекта. Такой просмотр выражается в виде компонентных реализаций.

### Процедура проектирования FPGA Express

FPGA Express выполняет три функции:

- Транслирует VHDL во внутренний формат

- Оптимизирует представление блокового уровня с помощью различных методов оптимизации

- Размещает логическую структуру проекта в определенной технологической библиотеке FPGA.

FPGA Express синтезирует VHDL описания в соответствии с *политикой синтеза* VHDL , описанной в Главе 2 «Стили описаний». Политика синтеза Synopsys VHDL имеет три части : методология проекта , стиль проекта и языковые конструкции. Политика синтеза используется для получения высококачественных VHDL-ориентированных проектов.

# Использование FPGA Express для компиляции проекта VHDL

Когда проект VHDL читается в FPGA Express , то он преобразуется во внутренний формат базы данных , так чтобы FPGA Express мог синтезировать и оптимизировать его. Когда FPGA Express оптимизирует проект , он может изменить структуру частей или всего проекта в целом. Вы управляете степенью реструктуризации. Предоставляются следующие опции :

- Полное сохранение иерархии проекта

- Разрешение перемещения целых модулей вверх или вниз по иерархии

- Разрешение комбинирования определенных модулей с другими

- Сжатие целого проекта в один модуль (сглаживание проекта), если это будет полезным.

В следующем разделе описана процедура проектирования , которая использует FPGA Express вместе с симулятором VHDL.

# Методология проектирования

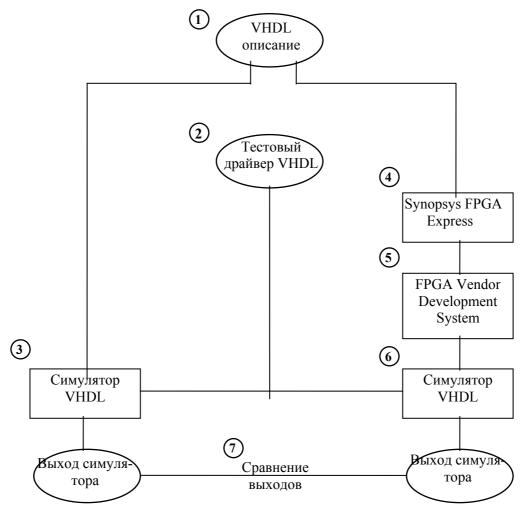

На рис.1-2 приведена типичная процедура проектирования , которая использует FPGA Express и симулятор VHDL. Каждый шаг такой модели проектирования описан подробно.

Рис.1-2. Блок-схема процесса проектирования.

1. Запись описания проекта на языке VHDL. Это описание может являться комбинацией структурных и функциональных элементов (как показано в Главе 2 «Стили описания»). Данное описание используется симуляторами FPGA Express и Synopsys VHDL.

- 2. Обеспечение языковых тестовых драйверов VHDL для симулятора. О правилах написания этих драйверов см. соответствующую главу в руководстве по симулятору. Драйвера обеспечивают тестовые вектора для моделирования и собирают выходные данные.

- 3. Моделирование проекта с помощью симулятора VHDL. Проверка правильности описания проекта.

- 4. Использование FPGA Express для синтеза и оптимизации описания проекта VHDL в элементарный список цепей. FPGA Express генерирует оптимизированные списки цепей , удовлетворяющие временным ограничениям выбранной архитектуры FPGA.

- 5. Использование вашей системы проектирования FPGA (у нас Design Manager) для связи определенной технологической версии FPGA с симулятором VHDL. Система проектирования включает в себя модели симуляции и интерфейсы , необходимые для сквозного проектирования.

- 6. Моделирование определенной технологической версии проекта с помощью симулятора VHDL. Вы можете использовать оригинальные драйверы моделирования VHDL из пункта 2, поскольку определения модулей и портов сохраняются в процессе трансляции и оптимизации.

- 7. Сравнение выхода моделирования на элементном уровне (пункт 6) с выходом моделирования оригинального описания VHDL (пункт 3) для проверки того, что исполнение является корректным.

# Глава 2. Стили описания

Стиль вашего первоначального описания VHDL оказывает основное воздействие на характеристики результирующего проекта элементного уровня, синтезируемого с помощью FPGA Express. Организация и стиль описания VHDL определяют базовую архитектуру вашего проекта. Вследствие того, что FPGA Express автоматизирует большинство решений логического уровня, используемых в вашем проекте, вы можете сконцентрироваться на оптимизации архитектуры. Вы можете применить некоторые высокоуровневые архитектурные решения, которые невозможны без использования FPGA Express. Определенные конструкции VHDL хорошо подходят для синтеза. Для применения таких решений и использования подобных конструкций вам необходимо ознакомиться со следующими понятиями:

- Иерархия проекта

- Типы данных

- Проектные ограничения

- Выбор регистра

- Асинхронные проекты

- Языковые конструкции

## Иерархия проекта

FPGA Express поддерживает иерархические границы , определяемые вами при использовании структурных конструкций VHDL. Эти границы приводят к двум основным результатам :

- 1. Каждый проектный объект , определяемый в описании VHDL , синтезируется отдельно и поддерживается в виде независимого проекта. При этом учитываются проектные ограничения , и каждый объект может быть оптимизирован отдельно в FPGA Express.

- 2. Компонентные реализации внутри описаний VHDL поддерживается в течение ввода. Имя реализации , которое вы присваиваете каждому пользовательскому объекту , сохраняется вплоть до выполнения на элементном уровне.

В Главе 3 обсуждаются объекты, а в Главе 7 - компонентные реализации.

Примечание: FPGA Express не поддерживает и не создает автоматически иерархию других неструктурных конструкций VHDL, таких как блоки, процессы, циклы, функции и процедуры. Эти элементы описания VHDL транслируются в контексте своих проектов. После чтения проекта VHDL вы можете сгруппировать вместе логику процесса, функции или процедуры внутри окна выполнения FPGA Express (Implementation Window).

Выбор иерархических границ оказывает значительное воздействие на качество синтезируемого проекта. С помощью FPGA Express вы можете оптимизировать проект , сохраняя его иерархиче-

ские границы. Тем не менее , FPGA Express только частично оптимизирует логику поперек иерархических модулей. Полная оптимизация возможна в тех частях иерархии проекта , которые сжаты в FPGA Express.

### Типы данных

В VHDL вы должны назначать тип всем портам, сигналам и переменным. Тип данных объекта определяется операцией, которая может быть ему назначена. Например, оператор AND определяется для объектов типа **BIT**, но не для объектов типа **INTEGER**. Типы данных, кроме того, важны при синтезе вашего проекта. Тип данных объекта определяет его размер (ширину в битах) и битовую организацию. Правильный выбор типов данных значительно улучшает качество проекта и помогает минимизировать количество ошибок.

См. Главу 4, в которой обсуждаются типы данных VHDL.

# Проектные ограничения

Вы можете описать качественные ограничения модуля проекта внутри FPGA Express Implementation Window. См. *Руководство пользователя FPGA Express* для более подробной информации.

# Выбор регистра

Размещение регистров и тактирующих схем являются очень важными архитектурными решениями. Существует два способа определения регистров в вашем описании VHDL. У каждого из этих методов существуют определенные преимущества :

- Вы можете реализовать регистры непосредственно в описании VHDL, выбрав любой нужный элемент из библиотеки FPGA. Тактирующие схемы могут быть произвольной сложности. Вы можете выбрать архитектуру, базирующуюся на триггерах или защелках. Основными недостатками такого подхода являются:

- Описание VHDL теперь привязано к определенной технологии , поскольку вы выбрали структурные элементы из технологической библиотеки. Однако , вы можете изолировать этот раздел вашего проекта в виде отдельного объекта , который затем будет связан с остальной частью проекта.

- Программа пишется более сложно.

- Вы можете использовать структуры **if** и **wait**, чтобы вывести триггера и защелки из вашего описания. Преимущества такого подхода прямо противоположны недостаткам предыдущего. При использовании логического описания регистра программа VHDL становится технологически независимой и более легкой для написания. Этот метод позволяет FPGA Express выбирать тип описываемого компонента в зависимости от ограничений. Таким образом, если необходим специфический компонент, должна использоваться его реализация. Тем не менее, некоторые типы регистров и защелок не могут быть описаны логически.

См. Главу 8, в которой обсуждается описание регистров.

### Асинхронные проекты

Вы можете использовать FPGA Express для конструирования асинхронных проектов с кратными и управляемыми синхроимпульсами. Однако , хотя эти проекты являются логически (статистически) корректными , они могут неправильно моделироваться или работать всвязи с условиями состязания.

### Языковые конструкции

Другим компонентом политики синтеза VHDL является набор конструкций, которые описывают ваш проект, определяют его архитектуру и дают последовательно хорошие результаты. В оставшейся части настоящего руководства описываются именно эти конструкции и их использование.

Понятия, упомянутые ранее в данной главе, описаны в руководстве следующим образом: Иерархия проекта

Глава 3 описывает применение и важность иерархии в проектах VHDL.

Глава 7 объясняет, как реализовать (применить) существующие компоненты.

Типы данных

Глава 4 описывает типы данных и их использование.

Выбор регистра

Вы можете реализовать регистры с помощью компонентных конструкций, описанных в Главах 3 и 7. Главы 6 и 8 описывают реализацию регистров через операторы VHDL if и wait.

# Глава 3. Описание проектов

Для описания проектов в VHDL вам необходимо ознакомиться со следующими понятиями:

- Объекты VHDL

- Конструкции VHDL

- Определение проектов

- Структурные проекты

### Объекты VHDL

Проекты , которые описываются в VHDL , состоят из объектов. *Объект* представляет собой один уровень иерархии проекта и может содержать полный проект , существующие аппаратные компоненты или VHDL-определенный объект.

Каждый проект состоит из двух частей: спецификации объектов и архитектуры. Спецификация объекта является его внешним интерфейсом. Архитектура объекта является его внутренним исполнением. У проекта есть только одна объектная спецификация (интерфейс), однако он может иметь несколько архитектур (исполнений). Когда объект компилируется в аппаратный проект, то конфигурация определяет используемую архитектуру. Объектная спецификация и архитектура могут содержаться в различных исходных файлах VHDL или в одном файле. В примере 3-1 показана объектная спецификация простого логического элемента (2-входовой И-НЕ).

Пример 3-1. Объектная спецификация VHDL

```

entity NAND2 is port(A, B: in BIT; — Два входа, A и В — Один выход, Z = (A and B)' end NAND2;

```

Примечание: В описаниях VHDL комментарии предваряются двумя дефисами (--). Все символы после этих дефисов до конца строки игнорируются FPGA Express. Единственными исключениями из этого правила являются комментарии, которые начинаются с -- pragma или -- synopsys; эти комментарии являются директивами FPGA Express.

Ключевое слово **entity** объявляет объектную спецификацию, этот объект может использоваться другими объектами проекта. Внутренняя архитектура объекта определяет его функцию.

В примерах 3-2 , 3-3 и 3-4 показаны три различных архитектуры для объекта **NAND2** . Три примера определяют эквивалентное исполнение **NAND2**. После оптимизации и синтеза каждое исполнение приводит к одинаковой схеме , вероятно к 2-входовому элементу И-НЕ выбранной технологии. Стиль описания архитектуры , используемый вами для данного объекта , зависит только от собственного предпочтения. В примере 3-2 показано , как объект **NAND2** может быть выполнен с помощью двух компонентов из технологической библиотеки. Входы объекта **A** и **B** соединяются с элементом И **U0** , что дает промежуточный сигнал **I**. Сигнал **I** затем соединяется с инвертором **U1** , обеспечивая выход объекта **Z**.

Пример 3-2. Структурная архитектура для объекта NAND2

```

architecture STRUCTURAL of NAND2 is

signal I: BIT;

component AND 2

-- Из технологии

library

port(I1, I2: in BIT;

O1: out BIT);

end component;

component INVERT -- Из технологии

library

port(I1: in BIT;

O1: out BIT);

end component;

begin

U0: AND_2 port map (I1 \Rightarrow A, I2 \Rightarrow B, O1 \Rightarrow I);

U1: INVERT port map (I1 \Rightarrow I, O1 \Rightarrow Z);

end STRUCTURAL;

В примере 3-3 показано, как вы можете определить объект NAND2 с помощью его логиче-

ской функции.

Пример 3-3. Архитектура потока данных для объекта NAND2

```

```

architecture DATAFLOW of NAND2 is

begin

Z \leq A nand B;

end DATAFLOW;

Пример 3-4. RTL архитектура для объекта NAND2

architecture RTL of NAND2 is

begin

process(A, B)

begin

if (A = '1') and (B = '1') then

Z \le 0;

else

Z <= '1';

end if;

end process;

```

end RTL;

# Конструкции VHDL

Высокоуровневые конструкции VHDL совместно работают для описания проекта. Описание состоит из :

Объектов

Интерфейсы с другими проектами.

Архитектур

Исполнения объектов проекта. Архитектуры могут определять связи с другими объектами через реализацию.

Конфигураций

Привязки объектов к архитектурам.

Процессов

Наборы последовательно выполняемых команд. Процессы объявляются внутри архитектур.

Подпрограмм

Алгоритмы, которые могут быть использованы более чем в одной архитектуре.

Блоков объявлений

Наборы объявлений, используемые одним или более проектами.

### Объекты

Проект VHDL состоит из одного или более объектов. Объекты имеют определенные входы и выходы и выполняют определенную функцию. Каждый проект состоит из двух частей : объектной спецификации и архитектуры. Объектная спецификация определяет входы и выходы проекта , а архитектура определяет его функцию.

Вы можете описать проект VHDL в виде одного или нескольких файлов. Каждый файл состоит из объектов , архитектур или блоков. Блоки определяют глобальную информацию , которая может использоваться различными объектами.

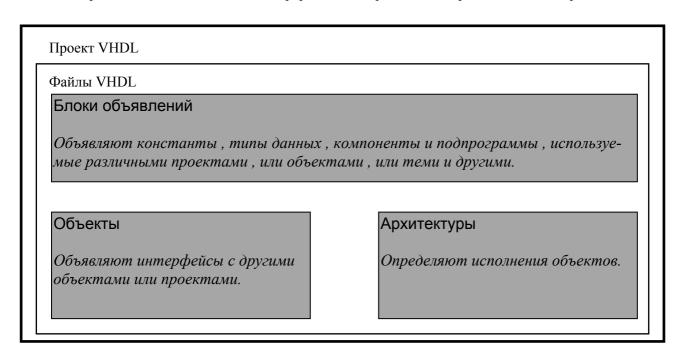

На рис.3-1 показана блок-схема иерархической организации проекта VHDL по файлам.

Рис.3-1. Организация проекта

# Архитектуры

Архитектура определяет функцию объекта. На рис.3-2 показана организация архитектуры. Не все архитектуры содержат каждую из приведенных конструкций.

Архитектура Объявления Объявляют сигналы , используемые для связи между параллельными операторами , а также между параллельными операторами и портами интерфейса. Объявляют типы , константы , компоненты и подпрограммы , используемые в архитектуре. Параллельные операторы Блоки Компонентные реализации Собирают вместе параллельные Создают экземпляр другого объекоператоры. ma. Сигнальные назначения Вычисляют значения и присваивают Процессы их сигналам. Определяют новый алгоритм. Вызовы процедур Вызывают предварительно определенный алгоритм.

Рис.3-2. Организация архитектуры.

Архитектура состоит из раздела объявлений, где вы объявляете сигналы, типы, константы, компоненты и подпрограммы, вслед за которым следует набор параллельных операторов.

Сигналы соединяют отдельные куски архитектуры (параллельные операторы) друг с другом , а также с внешним миром - через порты интерфейса. Вы объявляете тип каждого сигнала , который означает тип данных , переносимых этим сигналом. Типы , константы , компоненты и подпрограммы, объявляемые в архитектуре , являются для нее локальными. Для использования этих объявлений более , чем в одном объекте или архитектуре , размещайте их в блоках объявлений , которые будут описаны позже в этой главе.

Каждый параллельный оператор в архитектуре определяет вычислительную единицу, которая читает сигналы, осуществляет вычисления на базе сигнальных значений и назначает вычисленные значения сигналам. Параллельные операторы вычисляют все значения одновременно. Хотя порядок параллельных операторов не влияет на порядок выполнения, операторы часто координируют свою работу посредством связи друг с другом через сигналы.

Существует пять типов параллельных операторов - блоки , сигнальные назначения , вызовы процедур , компонентные реализации и процессы. Их можно описать следующим образом :

блоки

Группируют вместе набор параллельных операторов.

сигнальные назначения

Назначают вычисленные значения сигналам или портам интерфейса. вызовы процедур

Вызывают алгоритмы, которые вычисляют и присваивают значения сигналам. компонентные реализации

Создают экземпляр объекта , связывая его интерфейсные порты с сигналами или портами интерфейса уже определенного объекта. См. раздел «Структурное проектирование» ниже в этой главе.

### процессы

Определяют последовательные алгоритмы, которые читают значения сигналов и вычисляют новые значения для присваивания другим сигналам. Процессы обсуждаются в следующем разделе.

Параллельные операторы описаны в Главе 7.

# Конфигурации

Конфигурация определяет одну комбинацию объекта и соответствующей ему архитектуры.

Примечание: FPGA Express поддерживает только конфигурации, которые соответствуют одному объекту высшего уровня с архитектурой.

# Процессы

Процессы содержат *последовательные операторы*, которые определяют алгоритмы. В противоположность параллельным операторам последовательные выполняются по порядку. Этот порядок позволяет вам выполнять пошаговые вычисления. Процессы читают и записывают значения сигналов и портов интерфейса для связи с остальной архитектурой и приложениями системы.

На рис.3-3 показана организация конструкций процесса. Процессы могут содержать не все перечисленные конструкции.

Процессы являются уникальными в том, что они ведут себя по отношению к остальной части проекта так же, как параллельные операторы, однако внутри они организованы последовательно. Кроме того, только процессы могут определять переменные для хранения промежуточных значений при последовательных вычислениях.

Поскольку операторы в процессах выполняются последовательно , существует несколько конструкций для управления порядком выполнения , например , операторы **if** и **loop**. Последовательные операторы описаны в  $\Gamma$ лаве 6.

### Подпрограммы

Подпрограммы , так же как процессы , используют последовательные операторы для определения алгоритмов , которые вычисляют значения. В противоположность процессам , однако , они не могут непосредственно читать или записывать сигналы остальной части архитектуры. Все связи осуществляются через интерфейс подпрограммы ; каждый вызов подпрограммы имеет свой собственный набор интерфейсных сигналов.

Существует два типа подпрограмм - функции и процедуры. Функция непосредственно возвращает одиночное значение. Процедура возвращает ноль или более значений через свой интерфейс. Подпрограммы являются полезными , если вам нужно выполнить повторяющиеся вычисления , особенно в различных частях архитектуры. Подпрограммы описаны в Главе 6.

Процесс

### Объявления

Внутренние переменные, которые хранят временные значения при последовательных вычислениях, такие как типы, константы, компоненты и подпрограммы, используемые локально.

Последовательные операторы

## Сигнальные назначения

Вычисляют значения и присваивают их сигналам.

# Вызовы процедур

Вызывают предварительно определенный алгоритм.

# Назначения переменных

Хранят промежуточные значения в переменных.

# Операторы if

Условно выполняют группу последовательных операторов.

### Операторы case

Выбирают для выполнения группу последовательных операторов.

# Операторы Іоор

Выполняют повторяющиеся операторы.

# Операторы next

Пропускают оставшуюся часть цикла.

# Операторы exit

Завершают выполнение цикла.

# Операторы wait

Ожидают тактирующего сигнала.

## Операторы null

Не выполняют никаких действий; это пустые операторы заполнения.

Рис.3-3. Организация процесса.

# Блоки объявлений

Вы можете объединить константы, типы данных, объявления компонентов и подпрограмм в блоке объявлений VHDL, который затем будет использоваться более, чем в одном проекте или объекте. На рис.3-4 показана типичная организация блока объявлений. Блок объявлений должен содержать как минимум одну из конструкций, перечисленных на рис.3-4:

- Константы в блоках часто объявляют параметры системного уровня, такие как ширина информационного канала.

- Объявления типов данных VHDL часто включаются в блок объявлений для объявления типов данных , используемых во всем проекте. Все объекты проекта должны иметь общие типы интерфейсов , например , общие типы адресной шины.

- Компонентные объявления определяют интерфейсы с объектами, которые могут быть реализованы в проекте.

- Подпрограммы определяют алгоритмы, которые могут быть вызваны из любого места проекта.

Блоки объявлений обычно являются достаточно общими , так что вы можете использовать их в различных проектах. Например , блок  $std\_logic\_1164$  определяет типы данных  $std\_logic$  и  $std\_logic$  vector .

# Блок объявлений Объявления констант Определяют значения констант, используемых в проектах. Компонентные объявления Объявляют типов Объявляют типов Объявляют типов Зуемых в проектах. Подпрограммы Объявляют интерфейсы для объектов проекта.

Рис.3-4. Типичная организация блока объявлений.

### Использование блока объявлений

Оператор **use** позволяет объекту использовать объявления из блока. Поддерживаемый синтаксис этого оператора следующий :

# use LIBRARY\_NAME.PACKAGE\_NAME.ALL; где

**LIBRARY\_NAME** - имя библиотеки VHDL , а **PACKAGE\_NAME** - имя включаемого блока объявлений. Оператор **use** обычно является первым в файле блока объявлений или спецификации объекта. Synopsys не поддерживает разные блоки объявлений с одинаковыми именами , если они существуют в различных библиотеках. Никакие два блока не могут иметь одинаковое имя.

### Структура блока объявлений

Блок объявлений состоит из двух частей - *объявления* и *тела* : объявление блока

Хранит *общую* информацию , включая объявления констант , типов и подпрограмм. тело блока

Хранит *частную* информацию , включая локальные типы и исполнения подпрограмм (тела).

Примечание: Если объявление блока содержит объявления подпрограмм, то соответствующее тело блока должно определять тела подпрограмм.

### Объявления блока

Объявления блока содержат информацию, необходимую одному или более объектам проекта. Эта информация включает объявления типов данных, объявления сигналов, объявления подпрограмм и объявления компонентов.

Примечание: Сигналы, объявленные в блоках, не могут совместно использоваться разными объектами. Если два объекта используют сигнал из данного блока, то каждый из них должен создавать свою собственную копию этого сигнала.

Хотя вы можете объявить всю эту информацию явно в каждом проектном объекте или системной архитектуре, часто более легким является объявление системной информации в отдельном блоке объявлений. Каждый объект системы может впоследствии использовать системный блок объявлений

Объявление блока имеет следующий синтаксис :

```

package package_name is

{ package_declarative_item }

end [ package_name ];

```

где *package\_name* - имя данного блока объявлений. Элемент *package\_declarative\_item* может быть любым из следующих :

- предложение use (для включения других блоков)

- объявление типа

- объявление подтипа

- объявление константы

- объявление сигнала

- объявление подпрограммы

- объявление компонента

В примере 3-5 приведены некоторые объявления блоков.

Пример 3-5. Простые объявления блока

```

package EXAMPLE is

```

Для использования приведенного выше примера объявлений добавьте оператор **use** в начале описания вашего проекта следующим образом :

```

use WORK.EXAMPLE.ALL;

```

```

entity . . . architecture . . .

```

Прочие примеры блоков и их объявлений приведены в блоках объявлений , обеспечиваемых Synopsys. Эти блоки перечислены в Приложении В.

### Тела блока объявлений

В телах блока объявлений содержатся конкретные исполнения подпрограмм, перечисленных в объявлении блока. Тем не менее, эта информация никогда не видна проектам или объектам, которые используют данный блок. Тела блока могут включать исполнения (тела) подпрограмм, объявленных в объявлении блока и во внутренне поддерживаемых подпрограммах.

Тело блока объявлений имеет следующий синтаксис :

```

package body package_name is

{ package_body_declarative_item }

end [ package_name ];

```

где *package\_name* - имя соответствующего блока объявлений. Элемент *package body declarative item* может быть любым из следующих :

- предложение **use**

- объявление подпрограммы

- тело подпрограммы

- объявление типа

- объявление подтипа

- объявление константы

Примеры объявлений и тел блоков вы можете увидеть в блоке **std\_logic\_arith** , поддерживаемым FPGA Express. Этот блок объявлений приведен в Приложении В.

# Определение проектов

Высокоуровневые конструкции, обсужденные выше в данной главе, включают в себя:

- объектные спецификации (интерфейсы)

- объектные архитектуры (исполнения)

- подпрограммы

# Объектные спецификации

Объектная спецификация определяет характеристики объекта, которые должны быть известны до того, как этот объект будет связан с другими объектами и компонентами. Например, перед тем, как вы соедините счетчик с другими объектами, вы должны определить количество и типы его входов и выходов. Объектная спецификация определяет порты (входы и выходы) объекта и имеет следующий синтаксис:

где *entity\_name* - имя объекта , *generic\_declarations* определяет локальные константы , используемые для установления размеров или синхронизации объекта , а *port\_declarations* определяет количество и тип входов и выходов.

Другие объявления не поддерживаются в объектной спецификации.

### Основные (Generics) объектные спецификации

Основные спецификации являются параметрами объекта. Generics могут определять битовую ширину компонентов (таких как сумматоры) или внутренние временные значения. Основные спецификации могут иметь значение по умолчанию. Значение не по умолчанию назначается только в тех случаях, когда объект реализован (см. «Оператор реализации компонента» далее в этой главе) или сконфигурирован (см. «Объектные конфигурации» далее в этой главе). Внутри объекта основные спецификации являются константами. Синтаксис объявлений generic declarations следующий:

```

generic(

[ constant_name : type [ := value ]

{ ; constant_name : type [ := value ] }

);

```

где *constant\_name* - имя константы generic , *type* - ранее определенный тип данных , а необязательный параметр *value* является значением *constant\_name* по умолчанию.

Примечание: FPGA Express поддерживает только целые (INTEGER) типы generics.

# Спецификации портов объекта

Синтаксис объявлений port declarations следующий:

```

port(

[ port_name : mode port_type

{ ; port_name : mode port_type}]

);

```

где *port\_name* - имя порта ; *mode* - in , out , inout или buffer ; а *port\_type* - ранее определенный тип данных. Существуют четыре режима работы порта :

in

Может осуществлять только чтение.

Out

Может только присваивать значение.

inout

Может осуществлять чтение и присваивать значение. Читаемое значение - это то , которое приходит на порт , а не то , которое ему назначается (если таковое имеется).

buffer

Аналогично режиму out , но может быть прочитан. Читаемое значение равно назначенному. Имеет только один источник (драйвер). Более подробную информацию о драйверах см. в разделе «Управляемые сигналы» в Главе 7.

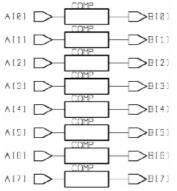

В примере 3-6 показана объектная спецификация для 2-входового N-битового компаратора с битовой шириной по умолчанию равной 8.

Пример 3-6. Интерфейс для N-битового компаратора.

```

-- Определяем объект (проект), называемый СОМР,

-- который имеет два N-битовых входа и один выход.

entity COMP is

generic(N: INTEGER := 8); -- по умолчанию 8 бит

port(X, Y: in BIT_VECTOR (0 to N-1);

EQUAL: out BOOLEAN);

end COMP;

```

Объектные архитектуры

Каждая объектная архитектура определяет одно исполнение функции объекта. Архитектуру можно классифицировать в диапазоне от алгоритма (набор последовательных операторов внутри процесса) до структурного списка цепей (набор компонентных реализаций). Архитектура имеет следующий синтаксис:

где architecture\_name - имя архитектуры , а entity\_name - имя реализуемого объекта. Элемент block declarative item может быть любым из следующих :

- предложение use

- объявление подпрограммы

- тело подпрограммы

- объявление типа

- объявление полтипа

- объявление константы

- объявление сигнала

- объявление компонента

Параллельные операторы (concurrent statement) описаны в главе 7.

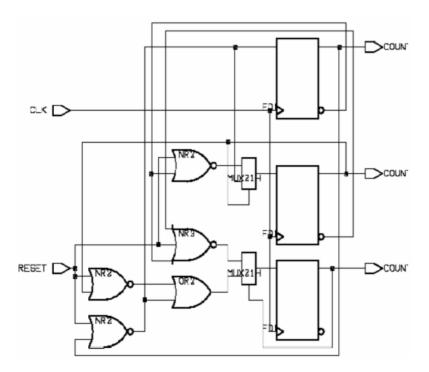

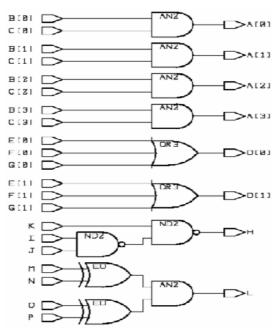

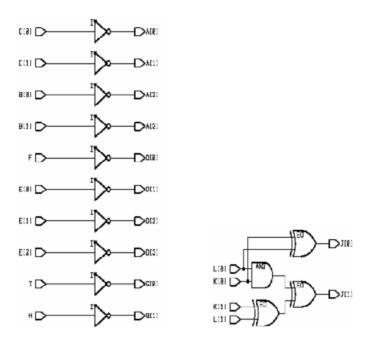

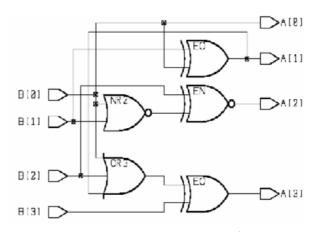

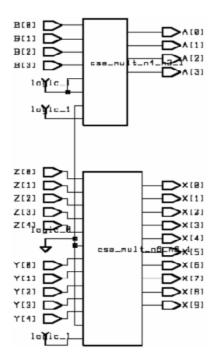

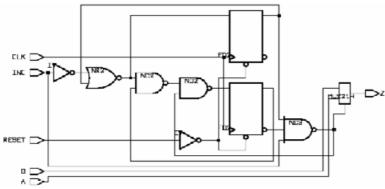

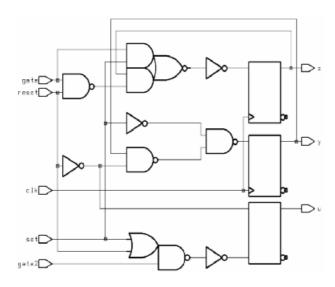

В примере 3-7 показано завершенное описание схемы трехбитового счетчика , объектная спецификация (COUNTER3) и архитектура ( $MY\_ARCH$ ). Этот пример также включает результирующую синтезированную схему.

Пример 3-7. Реализация трехбитового счетчика.

```

entity COUNTER3 is

port ( CLK:

in bit:

RESET:

in bit:

COUNT:

out integer range 0 to 7);

end COUNTER3;

architecture MY ARCH of COUNTER3 is

signal COUNT tmp: integer range 0 to 7;

begin

process

begin

wait until (CLK'event and CLK = '1');

-- ожидаем синхроимпульс

if RESET = '1' or COUNT tmp = 7 then

-- Ck. для сброса или макс. числа

COUNT_tmp <= 0;

else COUNT tmp <= COUNT tmp + 1;

-- продолжаем считать

end if:

end process;

COUNT <= COUNT tmp;

end MY_ARCH;

```

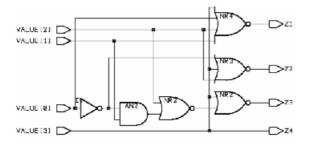

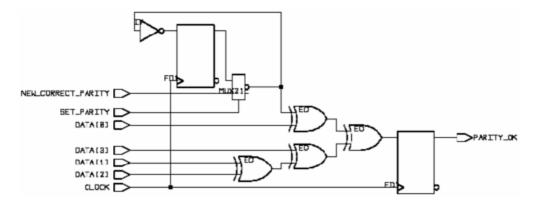

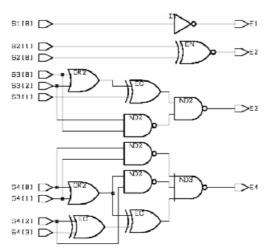

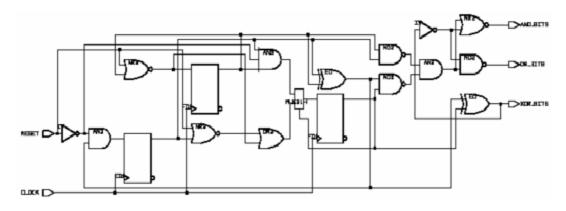

Рис.3-5. Схема трехбитового счетчика.

Примечание: В архитектуре вы не должны объявлять константы или сигналы под теми же именами, что и порты объекта. Если вы объявляете константу или сигнал с именем порта, то новое объявление «спрячет» имя порта. Если новое объявление включено в объявление архитектуры, (как показано в примере 3-8), а не во внутренний блок, FPGA Express даст отчет об ошибке.

Пример 3-8. Некорректное использование имени порта при объявлении сигналов или констант.

```

entity X is

port(SIG, CONST: in BIT;

OUT1, OUT2: out BIT);

end X;

architecture EXAMPLE of X is

signal SIG: BIT;

constant CONST: BIT := '1';

begin

end EXAMPLE;

Сообщения об ошибках, генерируемые для примера 3-8:

signal SIG: BIT;

Error: (VHDL-1872) line 13

Illegal redeclaration of SIG. (Некорректное переобъявление SIG).

constant CONST: BIT := '1';

Error: (VHDL-1872) line 14

Illegal redeclaration of CONST. (Некорректное переобъявление CONST).

```

# Объектные конфигурации

end [ configuration name ];

Конфигурация определяет одну комбинацию объекта и архитектуры для проекта.

Примечание: FPGA Express поддерживает только конфигурации, которые соответствуют одному объекту верхнего уровня с архитектурой.

Поддерживаемый синтаксис конфигурации следующий: configuration configuration\_name of entity\_name is for architecture\_name end for;

где *configuration\_name* - имя данной конфигурации , *entity\_name* - имя высокоуровневого объекта , a *architecture\_name* - имя архитектуры , используемой для *entity\_name*. В примере 3-9 показана конфигурация для трехбитового счетчика из примера 3-7. Эта конфигурация соответствует объектной спецификации счетчика (COUNTER3) с архитектурой (MY ARCH).

Пример 3-9. Конфигурация счетчика из примера 3-7.

```

configuration MY_CONFIG of COUNTER3 is

for MY_ARCH

end for;

end MY_CONFIG;

```

Примечание: Если вы не определяете конфигурацию для объекта с несколькими архитектурами, IEEE VHDL считает, что используется последняя прочитанная архитектура. Это определяется из файла .mra (самого последнего из проанализированных).

# Подпрограммы

Подпрограммы описывают алгоритмы, которые предполагается использовать более, чем в одном проекте. В отличие от операторов компонентных реализаций, когда подпрограмма используется объектом или другой подпрограммой, новый уровень иерархии проекта не создается автоматически. Тем не менее вы можете вручную определить подпрограмму как новый уровень проектной иерархии в окне исполнения FPGA Express (Implementation Window).

Два типа подпрограмм, процедуры и функции, могут содержать ноль или более параметров: процедуры

Процедуры возвращают не значение, а информацию вызывающим операторам об изменении значений их собственных параметров.

функции

Функция имеет одиночное значение, которое возвращается вызывающему оператору, однако она не может изменить значения этих параметров.

Так же, как и объект, подпрограмма состоит из двух частей - объявления и тела: объявление

Объявляет интерфейс к подпрограмме : ее имя , параметры и возвращаемое значение (если таковое имеется).

тело

Определяет алгоритм, который обеспечивает ожидаемый от подпрограммы результат. Когда вы объявляете подпрограмму в блоке объявлений, это объявление должно находиться в объявлении блока, а тело подпрограммы должно находиться в теле блока объявлений. Подпрограмма, объявляемая внутри архитектуры, имеет тело, но не имеет соответствующего объявления подпрограммы.

### Объявления подпрограмм

В объявлении подпрограммы перечисляются имена и типы ее параметров , а для функций - тип возвращаемого значения.

Синтаксис объявления процедуры имеет следующий вид:

```

procedure proc_name [ ( parameter_declarations ) ] ;

```

где *proc\_name* - имя процедуры.

Синтаксис объявления функции имеет следующий вид:

```

function func_name [ ( parameter_declarations ) ]

return type name;

```

где *func\_name* - имя функции , а *type\_name* - тип возвращаемого функцией значения. Синтаксис *parameter\_declarations* такой же , как и *port\_declarations* :

```

[ parameter_name : mode parameter_type

{ ; parameter_name : mode parameter_type}]

```

где *parameter\_name* - имя параметра ; *mode* - in , out , inout или buffer ; *parameter\_type* - panee определенный тип данных.

Параметры процедуры могут использовать любой режим. Параметры функции должны использовать только режим **in**. Сигнальные параметры диапазонного типа не могут быть пропущены через подпрограмму. В примере 3-10 показаны образцы объявлений для функции и процедуры.

Пример 3-10. Два объявления подпрограммы.

```

type BYTE is array (7 downto 0) of BIT; type NIBBLE is array (3 downto 0) of BIT;

```

$function\ IS\_EVEN(NUM:\ in\ INTEGER)\ return\ BOOLEAN;$

-- Возвращает TRUE, если NUM четный.

procedure BYTE\_TO\_NIBBLES(B: in BYTE;

**UPPER, LOWER:** out NIBBLE);

-- Разбивает BYTE на две половины : UPPER и LOWER.

Примечание: Когда вы вызываете подпрограмму, действительные параметры заменяются объявленными формальными параметрами. Действительные параметры либо являются постоянной величиной, либо именем сигнала, переменной, константы или порта. Действительный параметр должен поддерживать тип и режим формального параметра. Например, входной порт не может быть использован как выходной действительный параметр, а константа может использоваться только в качестве входного действительного параметра.

В примере 3-11 показаны некоторые вызовы подпрограмм, объявленных в примере 3-10.

Пример 3-11. Два вызова подпрограммы.

```

signal INT: INTEGER;

variable EVEN: BOOLEAN;

...

INT <= 7;

EVEN:= IS_EVEN(INT);

...

variable TOP, BOT: NIBBLE;

...

BYTE_TO_NIBBLES("00101101", TOP, BOT);

Тела подпрограмм

```

Тело подпрограммы определяет выполнение ее алгоритма. Синтаксис тела процедуры имеет следующий вид :

```

procedure procedure name [ (parameter declarations)

] is

{ subprogram declarative item }

begin

{ sequential statement }

end [ procedure name ];

Синтаксис тела функции имеет следующий вид:

function function name [ (parameter declarations) ]

return type name is

{ subprogram_declarative_item }

begin

{ sequential statement }

end [function name];

```

Элемент subprogram declarative item может быть любым из следующих:

- предложение use

- объявление типа

- объявление полтипа

- объявление константы

- объявление переменной

- объявление атрибута

- спецификация атрибута

- объявление подпрограммы

- тело подпрограммы

В примере 3-12 приведены тела подпрограмм, объявленных в примере 3-10.

Пример 3-12. Два тела подпрограмм.

```

function IS EVEN(NUM: in INTEGER)

return BOOLEAN is

begin

return ((NUM rem 2) = 0);

end IS EVEN;

procedure BYTE TO NIBBLES(B:

in BYTE;

UPPER, LOWER:

out NIBBLE) is

begin

UPPER := NIBBLE(B(7 downto 4));

LOWER := NIBBLE(B(3 downto 0));

end BYTE TO NIBBLES;

```

### Перегрузка подпрограмм

Вы можете перегрузить подпрограммы; более, чем одна подпрограмма может носить одинаковое имя. Каждая подпрограмма, которая использует данное имя, должна иметь различный профиль параметров. Последний определяет номер подпрограммы и тип параметров. Эта информация указывает на то, какая из подпрограмм вызывается в том случае, если несколько из них имеют одинаковые имена. Перегружаемые функции, кроме того, отличаются типом возвращаемых значений. В примере 3-13 показаны две подпрограммы с одинаковыми именами, но различными профилями параметров.

Пример 3-13. Перегрузка подпрограмм.

```

type SMALL is range 0 to 100;

```

```

type LARGE is range 0 to 10000;

function IS_ODD(NUM: SMALL) return BOOLEAN;

function IS_ODD(NUM: LARGE) return BOOLEAN;

signal A_NUMBER: SMALL;

signal B: BOOLEAN;

...

B <= IS_ODD(A_NUMBER); -- Вызывает первую из описанных выше функций

```

### Перегрузка операторов

Предопределенные операторы , такие как + , and и mod также могут быть перегружены. С помощью перегрузки вы можете адаптировать предопределенные операторы для работы с вашими собственными типами данных. Например , вы можете объявить новые логические типы вместо того , чтобы использовать предопределенные BIT и INTEGER . Однако , вы не можете использовать предопределенные операторы с этими новыми типами , пока для них не будут объявлены перегруженные операторы. В примере 3-14 показано , как некоторые предопределенные операторы перегружаются для нового логического типа.

```

Пример 3-14. Перегрузка операторов.

type NEW_BIT is ('0', '1', 'X');

— Новый логический тип

function "and"(I1, I2: in NEW_BIT) return NEW_BIT;

function "or" (I1, I2: in NEW_BIT) return NEW_BIT;

— Объявляем перегруженные операторы для нового логического типа

...

signal A, B, C: NEW_BIT;

...

C <= (A and B) or C;

```

При объявлении перегруженного типа VHDL требует заключать его имя или символ в двойные кавычки, поскольку в данном случае он является инфиксным оператором (т.е. используется между операндами). Если вы объявите перегруженные операторы без двойных кавычек, компилятор VHDL воспримет их как функции раньше, чем как операторы.

### Объявления типов

Объявления типов определяют имя и характеристики типа. Типы и их объявления полностью описаны в Главе 4. Тип - это именованный набор значений, таких как набор целых или набор (red, green, blue). Объект данного типа, такой как сигнал, может принимать любые имеющиеся в нем значения. В примере 3-14 показано объявление типа NEW\_BIT, а также некоторых функций и переменных этого типа.

Объявления типов разрешены в архитектурах , блоках объявлений , объектах , блоках , процессах и подпрограммах.

### Объявления подтипов

Используйте объявления подтипов для обозначения имени и характеристик ограниченного подмножества другого типа или подтипа. Подтип является полностью совместимым с родительским типом, но только в определенном диапазоне. Объявления подтипов описаны в Главе 4. В следующем объявлении подтипа (NEW\_LOGIC) определяется поддиапазон типа, объявленного в примере 3-14.

```

subtype NEW_LOGIC is NEW_BIT range '0' to '1';

Перевод: pep 27

```

Объявления подтипов разрешены там же, где и объявления подтипов : в архитектурах, блоках объявлений, объектах, блоках, процессах и подпрограммах.

### Объявления констант

Объявления констант создают именованные значения данного типа. Значение константы может быть прочитано , но не изменено. Объявления констант разрешены в архитектурах , блоках объявлений , объектах , блоках , процессах и подпрограммах. В примере 3-15 показаны некоторые объявления констант.

Пример 3-15. Объявления констант.

constant WIDTH : INTEGER := 8; constant X : NEW BIT := 'X';

Вы можете использовать константы в выражениях, как описано в Главе 5, а также в качестве исходных значений в операторах присваивания, как описано в Главе 6.

### Объявления сигналов

Объявления сигналов создают новые именованные сигналы (проводники) данного типа. Сигналам могут быть присвоены начальные значения (по умолчанию). Однако , эти начальные значения не используются для синтеза. Сигналы с несколькими источниками (сигналы , управляемые присоединенной логикой) могут иметь соответствующие функции разрешения , как описано в следующем разделе. В примере 3-16 показано два объявления сигналов.

Пример 3-16. Объявления сигналов.

signal A, B : BIT; signal INIT : INTEGER := -1;

Примечание: Порты также являются сигналами, у которых есть ограничения: выходные порты не могут быть прочитаны, а входным не может быть присвоено значение. Сигналы создаются либо через объявления портов, либо через объявления сигналов. Порты создаются только через объявления портов.

Вы не можете объявлять сигналы в архитектурах , объектах и блоках , а также использовать их в процессах и подпрограммах. Процессы и подпрограммы не могут объявлять сигналы для внутреннего использования.

Вы можете использовать сигналы в выражениях, как описано в Главе 5. Значения назначаются сигналам с помощью операторов присвоения, описанных в Главе 6.

## Функции разрешения

Функции разрешения используются с сигналами , которые могут быть связаны (соединены вместе). Например , если к сигналу непосредственно подсоединены два источника (драйвера) , функция разрешения устанавливает , является ли значение сигнала функцией И , ИЛИ или функцией третьего состояния от значений источников. Для моделирования вы можете записать произвольную функцию , чтобы избежать шинных конфликтов.

Примечание: Функция разрешения может изменить значение разрешаемого сигнала, даже если все источники имеют одинаковое значение.

Функция разрешения сигнала является частью объявления подтипа этого сигнала. Разрешаемый сигнал создается за четыре шага :

```

-- Шаг 1

type SIGNAL_TYPE is ...

-- базовый тип сигнала SIGNAL_TYPE

-- Шаг 2

subtype res_type is res_function SIGNAL_TYPE;

-- имя подтипа res_type

-- имя функции res_function

-- тип сигнала res_type (подтип от SIGNAL_TYPE)

...

-- Шаг 3

function res_function (DATA: ARRAY_TYPE)

return SIGNAL_TYPE is

-- объявление функции разрешения

-- ARRAY_TYPE должен быть безусловным подмножеством SIGNAL_TYPE

...

-- Шаг 4

signal resolved_signal_name:res_type;

-- resolved_signal_name - разрешаемый сигнал

```

- 1. Объявляется базовый тип сигнала.

- 2. Подтип разрешаемого сигнала объявляется как подтип базового типа и включает имя функции разрешения.

- 3. Объявление самой функции разрешения (и далее ее определение).

- 4. Разрешаемые сигналы объявлены как разрешаемые подтипы.

FPGA Express не поддерживает произвольные функции разрешения. Разрешены только AND , OR и функция третьего состояния. FPGA Express требует , чтобы вы помечали все функции разрешения специальной директивой , показывающей тип выполняемого разрешения.

Примечание: FPGA Express учитывает директивы только при окончательной разводке аппаратного обеспечения. Тело функции разрешения анализируется, но игнорируется. Использование не поддерживаемых конструкций VHDL (см. Приложение С) приводит к генерации ошибки. Не соединяйте сигналы, которые используют различные функции разрешения. FPGA Express поддерживает только одну функцию разрешения на цепь.

Существует три директивы функций разрешения :

- -- synopsys resolution method wired and

- -- synopsys resolution method wired or

- -- synopsys resolution\_method three\_state

Примечание: Результаты моделирования до и после синтеза могут не согласовываться между собой, если тело функции разрешения, используемой симулятором, не совпадает с директивой, используемой синтезатором.

В примере 3-17 показано , как создать и использовать разрешаемые сигналы , а также применение директив компилятора для функций разрешения. Базовым типом сигнала является предопределенный тип **ВІТ**.

Пример 3-17. Разрешаемый сигнал и его функция разрешения.

```

package RES_PACK is

function RES_FUNC(DATA: in BIT_VECTOR) return BIT;

subtype RESOLVED_BIT is RES_FUNC BIT;

end;

package body RES_PACK is

function RES_FUNC(DATA: in BIT_VECTOR) return BIT

is

Перевод: рер 29

```

```

-- pragma resolution method wired and

begin

-- Код данной функции игнорируется FPGA,

Express

-- однако анализируется на предмет корректного синтаксиса VHDL

for I in DATA'range loop

if DATA(I) = '0' then

return '0';

end if:

end loop:

return '1';

end;

end:

use work.RES_PACK.all;

entity WAND VHDL is

port(X, Y: in BIT; Z: out RESOLVED BIT);

end WAND VHDL;

architecture WAND VHDL of WAND VHDL is

begin

Z \leq X;

Z \leq Y;

end WAND_VHDL;

```

# Объявления переменных

Объявления переменных определяют именованное значение данного типа. Вы можете использовать переменные в выражениях , как описано в Главе 5. Переменным присваиваются значения с помощью операторов присвоения , описанных в главе 6. В примере 3-18 показаны некоторые объявления переменных.

Пример 3-18. Объявления переменных.

variable A, B: BIT; variable INIT: NEW BIT;

Примечание: Переменные объявляются и используются только в процессах и подпрограммах, так как процессы и подпрограммы не могут объявлять сигналы для внутреннего использования.

### Структурное проектирование

FPGA Express работает с одним или несколькими проектами. Каждый объект (и архитектура) в описании VHDL транслируется в одиночный проект в FPGA Express. Кроме того , в оригиналах проекты могут находиться в отличных от VHDL форматах , таких как уравнения , программируемые логические матрицы (PLA) , машинные состояния , другие языки HDL или списки цепей. Проект может содержать низкоуровневые объекты , соединенные цепями (сигналами) с низкоуровневыми портами проекта. Такие низкоуровневые проекты могут содержать и другие объекты из проектов VHDL , проектов , представленных в каких-либо других форматах Synopsys или ячеек из технологической библиотеки. Реализуя проекты внутри проектов , вы создаете иерархию.

Иерархия в VHDL определяется через использование объявлений компонентов и операторов компонентной реализации. Для включения проекта вы должны определить его интерфейс вместе с

объявлением компонентов. Затем вы можете создать реализацию данного проекта с помощью *опера- тора* компонентной реализации. Если ваш проект содержит только объекты VHDL, то каждый оператор объявления компонента соответствует объекту в проекте. Если ваш проект использует другие проекты или ячейки из технологической библиотеки, не описанные в VHDL, создаются объявления компонентов без соответствующих объектов. Затем вы можете использовать FPGA Express для связи VHDL компонента с не-VHDL проектом или ячейкой.

Примечание: Для моделирования вашего проекта VHDL вы должны обеспечить описания объявлений объектов и архитектур для всех компонентных объявлений.

# Использование компонентов аппаратного уровня

VHDL включает конструкции для использования существующих аппаратных компонентов. Такие структурные конструкции могут быть использованы для определения списка цепей компонентов. В следующих разделах описано , как использовать компоненты , и как FPGA Express конфигурирует эти компоненты.

### Компонентные объявления

Вы должны объявить компонент в архитектуре или блоке объявлений до того , как использовать (реализовать) его. Оператор компонентного объявления аналогичен оператору объектной спецификации , описанному ранее , в котором определяется компонентный интерфейс. Компонентное объявление имеет следующий синтаксис :

где *identifier* - имя данного типа компонента , а синтаксис элементов *generic\_declarations* и *port\_declarations* такой же , как у определенных ранее для объектных спецификаций. В примере 3-19 показан простой оператор компонентного объявления.

Пример 3-19. Компонентное объявление двухвходового элемента И.

```

component AND2

port(I1, I2: in BIT;

O1: out BIT);

end component;

```

В примере 3-20 показан оператор компонентного объявления , который использует общий (generic) параметр.

Пример 3-20. Компонентное объявление N-битового сумматора.

```

component ADD generic(N: POSITIVE);

port( X, Y: in BIT_VECTOR(N-1 downto 0);

Z: out BIT_VECTOR(N-1 downto 0);

CARRY: out BIT)

end component;

```

Хотя оператор компонентного объявления аналогичен объектной спецификации , он служит другой цели. Компонентное объявление требуется тля того , чтобы объект **AND2** или **ADD** стал применимым , или видимым , внутри архитектуры. После объявления компонента он может быть использован в проекте.

### Источники компонентов

Объявленный компонент может находиться в том же файле описания VHDL , другом файле VHDL , другом формате (например , формате обмена электронными данными - EDIF) или таблице состояний , а также в технологической библиотеке. Если компонента нет ни в одном из текущих исходных файлов VHDL , он должен быть уже откомпилирован FPGA Express. Когда проект , который использует компоненты , компилируется FPGA Express , то предварительно откомпилированные компоненты ищутся по имени в следующем порядке :

- 1. В текущем проекте.

- 2. Во входном исходном файле или файлах, идентифицированных в окне исполнения FPGA Express.

- 3. В библиотеках специфических технологических компонентов FPGA.

### Совместимость портов компонента

FPGA Express проверяет совместимость объектов VHDL. Для других объектов имена портов берутся из оригинального описания проекта.

- Для компонентов из технологической библиотеки именами портов являются имена входных и выходных выводов.

- Для проектов EDIF именами портов являются имена портов EDIF.

Битовая ширина каждого порта также должна быть согласована. FPGA Express проверяет совместимость для компонентов VHDL , потому что типы портов должны быть идентичными. Для компонентов из других источников FPGA Express осуществляет проверку при линковании компонента в описание VHDL.

# Оператор реализации компонента

Оператор компонентной реализации исполняет и связывает компоненты для формирования структурного описания (списка цепей) проекта. Оператор реализации компонента может создавать новый уровень иерархии проекта , он имеет следующий синтаксис :

где *instance\_name* - имя реализации компонента типа *component\_name*. Необязательный элемент generic map назначает иные , чем по умолчанию , общие значения. Каждый элемент generic\_name является именем generic , точно так же , как указывалось в соответствующем операторе объявления компонента. Каждое выражение *expression* представляет соответствующее значение. port map назначает порты для связей компонента. Каждое имя port\_name является именем порта , точно так же, как указывалось в соответствующем операторе объявления компонента. Каждое выражение *expression* представляет значение сигнала.

FPGA Express использует следующие два правила для решения , какой объект и архитектуру ассоциировать с реализацией компонента :

- 1. Каждое объявление компонента должно иметь объект с таким же именем : объект VHDL , проект из другого источника (в другом формате) или библиотеку компонентов. Этот объект используется для каждой компонентной реализации , соответствующей объявлению компонента.

- 2. Если объект VHDL имеет более, чем одну архитектуру, то для каждой компонентной реализации, соответствующей объявлению компонента, используется *последняя* введенная архитектура. Файл .mra определяет последнюю проанализированную архитектуру.

### Размещение значений Generic

При реализации компонента с общими значениями (generics) вы можете присвоить им определенные значения. Если у generic нет значения по умолчанию, то они должны реализовываться с параметром **genericmap**. Например, четырехбитовая реализация компонента **ADD** из примера 3-20 должна использовать следующий **genericmap**:

```

U1: ADD genericmap (N => 4)

port map (X, Y, Z, CARRY...);

```

port map назначает порты компонента действительным сигналам; это описано в следующем разделе.

### Размещение связей портов

Вы можете определить связи портов в операторах компонентной реализации как при помощи нужного поименования , так и при помощи соответствующего расположения. При использовании именованной записи конструкция *port\_name* => идентифицирует определенные порты компонента. При использовании позиционной записи выражения для портов компонента просто перечисляются в порядке объявления. В примере 3-21 показана именованная и позиционная запись оператора компонентной реализации для U5.

Пример 3-21. Эквивалентные именованная и позиционная записи.

```

U5: or2 port map (O => n6, I1 => n3, I2 => n1);

-- Именованная запись

U5: or2 port map (n3, n1, n6);

-- Позиционная запись

```

Примечание: Когда вы используете позиционную запись, то реализуемые выражения (сигналы) для порта должны следовать в том же порядке, как при объявлении портов.

В примере 3-22 показано структурное описание (список цепей) для объекта **COUNTER3** из примера 3-7.

Пример 3-22. Структурное описание трехбитового счетчика.

```

architecture STRUCTURE of COUNTER3 is

component DFF

port(CLK, DATA: in BIT;

O: out BIT);

end component;

component AND2

port(I1, I2: in BIT;

O: out BIT);

end component;

component OR2

port(I1, I2: in BIT;

O: out BIT);

end component;

component NAND2

port(I1, I2: in BIT;

O: out BIT);

end component;

component XNOR2

port(I1, I2: in BIT;

O: out BIT);

end component;

component INV

```

```

port(I: in BIT;

O: out BIT);

end component;

signal N1, N2, N3, N4, N5, N6, N7, N8, N9: BIT;

begin

u1: DFF port map(CLK, N1, N2);

u2: DFF port map(CLK, N5, N3);

u3: DFF port map(CLK, N9, N4);

u4: INV port map(N2, N1);

u5: OR2 port map(N3, N1, N6);

u6: NAND2 port map(N1, N3, N7);

u7: NAND2 port map(N6, N7, N5);

u8: XNOR2 port map(N8, N4, N9);

u9: NAND2 port map(N2, N3, N8);

COUNT(0) \leq N2;

COUNT(1) \le N3;

COUNT(2) \leq N4;

end STRUCTURE;

```

### Технологически независимая реализация компонента

При использовании структурного стиля проектирования вы можете захотеть реализовать многие логические компоненты. Для этих целей Synopsys обеспечивает общую технологическую библиотеку **GTECH**. В этой библиотеке содержатся технологически независимые логические компоненты , такие как :

- элементы И, ИЛИ и исключающее ИЛИ (2, 3, 4, 5 и 8 входов)

- однобитовые сумматоры и полусумматоры

- схемы приоритета 2-из-3

- мультиплексоры

- триггера и защелки

- многоуровневые логические элементы, такие как И-НЕ, И-ИЛИ, И-ИЛИ-НЕ

Вы можете использовать эти простые компоненты для создания технологически независимых проектов. В примере 3-23 показано , как N-битовый сумматор с переносом может быть создан из N однобитовых сумматоров.

Пример 3-23. Проект, использующий технологически независимые компоненты.

```

library GTECH;

use gtech.gtech components.all;

entity RIPPLE CARRY is

generic(N: NATURAL);

in BIT VECTOR(N-1 downto 0);

port(

A, B:

CARRY IN:

in BIT;

out BIT VECTOR(N-1 downto 0);

SUM:

CARRY OUT: out BIT;);

end RIPPLE_CARRY;

architecture TECH INDEP of RIPPLE CARRY is

signal CARRY: BIT VECTOR(N downto 0);

begin

CARRY(0) \le CARRY IN;

```

# Глава 4. Типы данных

VHDL является строго типизированным языком. Каждая константа, сигнал, переменная, функция и параметр объявляются с определенным типом, таким как **BOOLEAN** или **INTEGER**, и могут хранить или возвращать значение только этого типа.